# Integration of Air-Gap Transmission Lines on Doped Silicon Substrates Using Glass Microbump Bonding Techniques

Jeff C. P. Chuang, *Student Member, IEEE*, and Samir M. El-Ghazaly, *Senior Member, IEEE*

**Abstract**—Air-gap transmission-line structures have been fabricated and integrated on doped silicon substrates using glass microbump bonding (GMBB) techniques. The air-gap transmission lines have the advantages of low losses and low dispersion compared to conventional uniplanar transmission lines on semiconductor substrate. This bonding technique provides an alternative approach for both monolithic microwave integrated circuits (MMIC's) and optoelectronic integrated circuits (OEIC's) on silicon substrates. To demonstrate the potential of air-gap structures, several transmission-line configurations are fabricated and tested. The measured data are compared with simulation results. The results confirm the air-gap structures low-loss capabilities. To further explore the advantage of this bonding technique, several spiral inductors are fabricated in air-gap configurations. Their measured characteristics demonstrate the low dispersion potential of this technology. Finally, the integration of air-gap interconnects for OEIC's on silicon CMOS circuitry is also proposed.

## I. INTRODUCTION

RAPID advances in semiconductor integrated technology coupled with the progress in both wireless and fiber-optic communications demand sustained improvements and developments of monolithic microwave integrated circuits (MMIC's) and optoelectronic integrated circuits (OEIC's) technology. The development of next-generation digital wireless communication systems is constrained by cost, size, and power considerations [1], which resulted in rapid growth in MMIC research to meet the increased performance demands [2], [3]. To meet the system level requirements, the current technology uses a combination of GaAs and silicon integrated circuits (IC's), which are wire bonded to high-performance passive components. Off-chip passive components often pose a size-limitation factor in many designs. MMIC's with on-chip matching and filter components can reduce size and cost compared to the hybrid approach [4]. Monolithic integration of passive components, on silicon bipolar junction transistor (BJT) or MOSFET IC's, can provide a cost-effective solution for complex mixed-signal applications [5]. However,

Manuscript received March 20, 1998; revised August 7, 1998. The work of J. C. P. Chuang was supported under a Motorola Partnership in Research Grant. This work was supported in part under U.S. Army Research Grant DAAH04-95-1-0252, and in part under ARPA/ARO Grant DAAH04-93-G-0248.

The authors are with the Department of Electrical Engineering, Center for Solid State Electronic Research, Arizona State University, Tempe, AZ 85287-5706 USA.

Publisher Item Identifier S 0018-9480(98)08342-2.

silicon IC processes need doped silicon substrate to achieve the desirable active-device performance. For short-channel MOSFET's, current fabrication processes require conductive substrates to reduce the “snapback effect” [6]. The conducting silicon substrate limits the performance of on-chip passive components, such as transmission lines, filters, inductors, and high-*Q* resonators.

For OEIC's, the potential of low-threshold and high-frequency GaAs vertical-cavity surface-emitting lasers (VCSEL's) [7], [8] has stimulated a tremendous amount of research and development in integrating VCSEL arrays with microelectronics and micro-optics [9]. Low-cost glass substrates are highly transparent over the 0.4–1.2- $\mu$ m region of the optical spectrum. The optical properties of the glass substrates made them essential components for most OEIC integration.

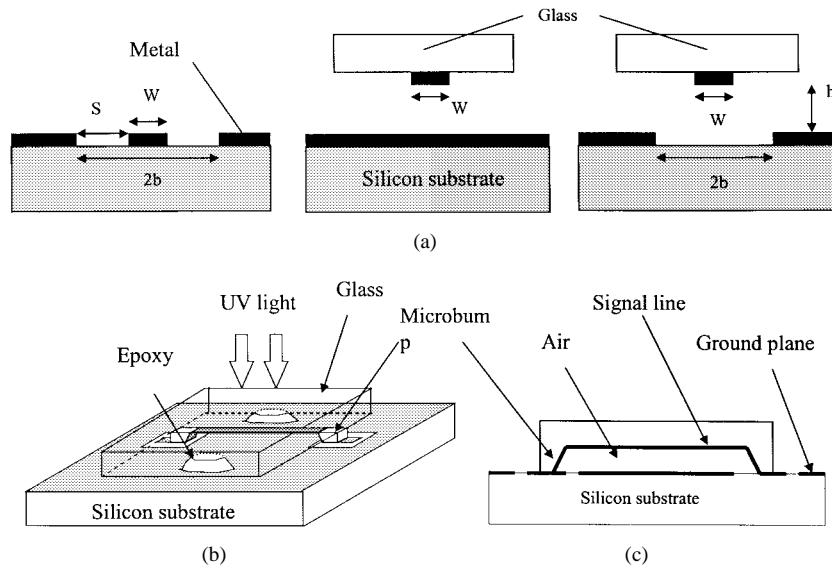

In this paper, we demonstrate a new technology for both MMIC's and OEIC's using glass substrates. Novel interconnects are developed on the glass substrates and connected to semiconductor substrates using the glass microbump bonding technique (GMBB), which is a new process developed to overcome some of the limitations in MMIC and OEIC integration. The new interconnects have their signal lines suspended in air. Therefore, they will be referred to as air-gap transmission lines. They enable several important advantages in MMIC's and OEIC's. To demonstrate these advantages, two types of air-gap transmission lines using the GMBB method are introduced: the air-gap microstrip line (AGML) and the air-gap coplanar waveguide (AGCPW). Fig. 1 shows the simplified cross-sectional view of a conventional coplanar waveguide (CPW) and the air-gap transmission lines. The air-gap height is precisely controlled using the glass microbump. The air-gap transmission lines on glass superstrate are integrated with silicon substrates. The recent successful demonstrations of passive components fabricated on silicon using micro-machining techniques and on high-resistivity silicon substrates show the feasibility of good performance MMIC's on low-cost silicon substrates [10], [11]. The main feature of the GMBB method presented in this paper is the use of conducting silicon substrates for MMIC applications.

At present, the most common interconnects used in monolithic IC technology are the microstrip and CPW configurations. The cross-sectional geometry of these interconnects change the propagating field distributions, which has a large

Fig. 1. (a) Cross-sectional view of the CPW, AGML, and AGCPW transmission-line configurations. (b) Simplified GMBB bonding process layout. (c) Cross-sectional view of the air-gap structure.

impact on the circuit performance. The losses and parasitic capacitances of the transmission lines on semiconductor substrates degrade the performance at high frequencies. Air-gap transmission lines using the GMBB method avoid these problems by having the propagating fields concentrated in air, which minimizes both the losses and parasitic capacitance effects.

This paper is organized as follows. Firstly, the characteristics of the AGML's and AGCPW's are theoretically investigated. Secondly, the process for fabricating these structures is outlined. The loss performance of air-gap interconnects is compared with conventional CPW on conducting silicon substrates. To further explore the advantages of air-gap transmission lines, several spiral inductors are fabricated using AGML's. The AGML inductor's performance is compared with the characteristics of conventional inductors. Finally, the integration of VCSEL's on CMOS circuitry for optoelectronic transmitter using the GMBB method is presented.

## II. MODELING AND DESIGN OF AIR-GAP INTERCONNECTS

Recently, transmission lines on semiconductor substrates have been investigated using solid-state physics concepts [12]. They are considered as Schottky (metal–semiconductor) junctions or metal–insulator–metal junctions. From the loss analysis, it is confirmed that high-frequency performance of interconnects on semiconductor substrates are affected by the semiconductor surface conditions, as well as the properties of bulk material. To model the electromagnetic (EM) wave propagation characteristics of transmission lines on semiconductor substrates, both the Poisson's equation and continuity equation are solved simultaneously to take into account the response of the electrons in the semiconductor material to the applied EM field [13].

Hence, modeling of transmission lines on semiconductor substrates requires detailed information about the semiconductor material and its properties. On the other hand, the

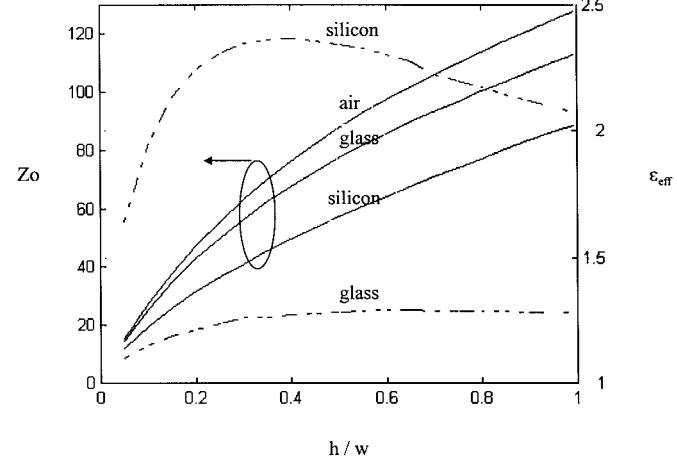

Fig. 2. Simulated characteristic impedance (solid lines) and effective dielectric constant (dashed lines) of AGML.

EM wave propagation characteristics of air-gap structures are considerably less affected by the properties of semiconductor substrates. Thus, they are easier to simulate. In this paper, the quasi-TEM mode propagation characteristics of the air-gap transmission lines are simulated using the SILVACO simulation package. Poisson's equation is solved to obtain the capacitance matrix of the structure. Using a similar structure, which is completely filled with air, the inductance matrix is calculated. Hence, the effective dielectric constants and characteristic impedance can be obtained.

For comparison purposes, both AGML and AGCPW structures are simulated under three different cases. In case one, a signal line is suspended in air without any cover material. In cases two and three, the signal lines are deposited on glass ( $\epsilon_r = 2.25$ ) and silicon ( $\epsilon_r = 12$ ) superstrates, respectively. The characteristics of AGML under these three cases are shown in Fig. 2. The characteristic impedance of this structure can be varied over a relatively wide range by controlling the air-gap height ( $h$ ) and signal line width

Fig. 3. Simulated characteristic impedance (solid lines) and effective dielectric constant (dashed lines) of AGCPW.

( $w$ ). The effective dielectric constant is very close to one, when the signal line is deposited on a glass superstrate. This case demonstrates the very low dispersion characteristics of this structure.

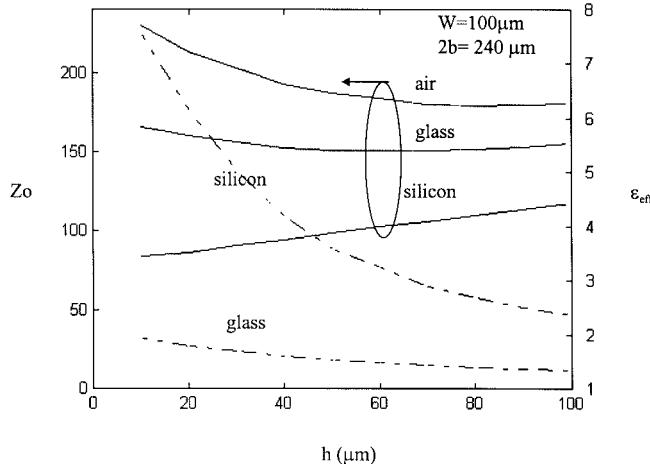

For the AGCPW structure, simulating its EM wave characteristics requires four independent variables, which include the signal line width ( $w$ ), air-gap height ( $h$ ), ground gap spacing ( $2b$ ), and substrate thickness. In this paper, the main emphasis is on reporting the advantage of air-gap structure using the GMBB method. Therefore, the example presented here has the following dimensions: fixed signal line width  $w = 100 \mu\text{m}$ ,  $2b = 240 \mu\text{m}$ , and infinite substrate thickness. Several air-gap heights  $h$  are used in this simulation. The properties of the AGCPW under these conditions are shown in Fig. 3.

Both air-gap structures have higher characteristic impedance compared to conventional transmission lines that are in same geometrical dimension since the field lines are mostly in air, which reduces the capacitance per unit length.

### III. FABRICATION OF AIR-GAP INTERCONNECTS

In order to characterize the microwave performance of both AGML and AGCPW transmission lines, several transmission lines are fabricated on glass substrates using the GMBB method. Fig. 1(b) and (c) illustrates a glass substrate bonded to a semiconductor substrate using the GMBB method. The fabrication process is described as follows. Firstly, a standard photolithography is used to pattern the bumps on a thin glass slide. Secondly, wet chemical etching using hydrofluoric (HF) acid is employed. Thus, several glass microbumps with different heights can be produced. Thirdly, the signal lines are deposited using  $E$ -beam evaporation. After a small amount of ultraviolet (UV) curable epoxy is applied onto the silicon substrate surface, the microbumps covered by metal lines on the glass superstrate are aligned to the signal launchers on semiconductor substrate with a regular UV contact aligner. Taking advantage of the glass substrate optical transparency in the UV region, the bonding processing is simply accomplished by UV exposure. It should be noted that in the transmission-line study, 2- $\mu\text{m}$ -thick aluminum is used for the signal lines.

However, in the inductor analysis presented later in this paper, 3- $\mu\text{m}$ -thick gold lines are used.

Three transmission-line structures are fabricated:

- 1) AGML;

- 2) AGCPW;

- 3) conventional CPW.

The silicon motherboards used in this paper have thickness of  $500 \mu\text{m}$  and resistivity of  $25 \Omega \cdot \text{cm}$ . For the AGML and AGCPW, the signal line width is  $100 \mu\text{m}$ , microbump height is  $15 \mu\text{m}$ , and line length is  $4400 \mu\text{m}$ . The only difference between the two air-gap configurations is the AGCPW has a ground spacing ( $2b$ ) of  $240 \mu\text{m}$ . For the conventional CPW, the signal line width ( $W$ ) is  $100 \mu\text{m}$ , line spacing ( $S$ ) is  $70 \mu\text{m}$ , and line length is  $5000 \mu\text{m}$ .

All transmission lines fabricated in this experiment include the microwave-launcher section at both ends of the lines. The microwave launcher has the conventional CPW configuration for  $150\text{-}\mu\text{m}$ -pitch CASCADE probes to perform on-wafer characterization. The launcher length is  $500 \mu\text{m}$ , of which  $200 \mu\text{m}$  is in contact with glass microbump.

## IV. MEASUREMENT

### A. Test Setup

The samples were first measured using HP4145A to extract the dc resistance values. The high-frequency measurement setup consists of an HP 8510A network analyzer with Cascade Microtech high-frequency ground-signal-ground coplanar probes and a computer to extract the  $S$ -parameters. For loss extraction, a short-open-load-through (SOLT) two-port calibration technique was performed.

### B. Measurement Results and Discussion

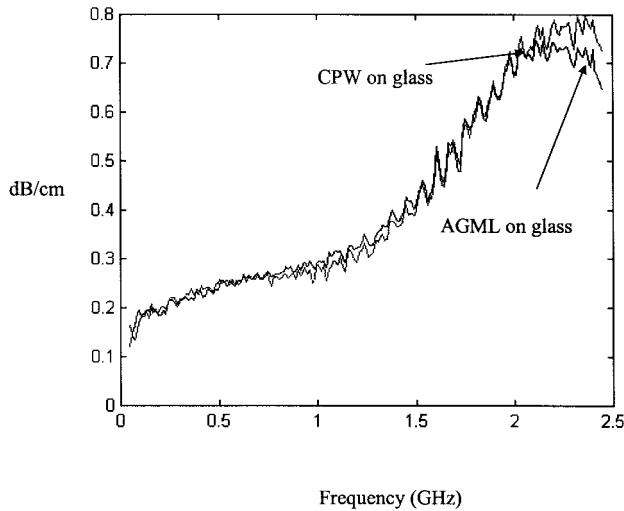

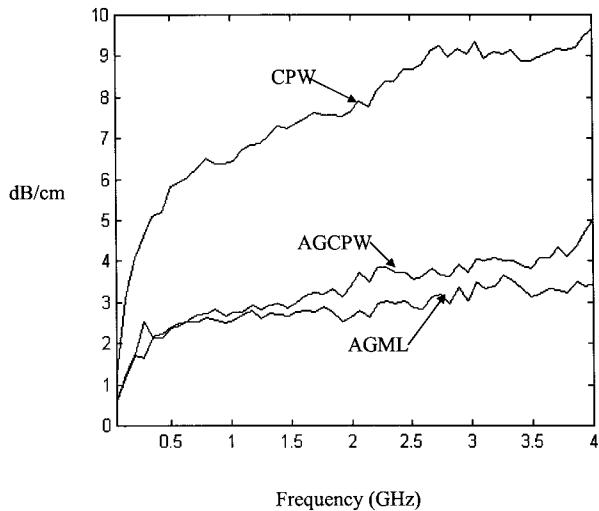

There are mainly two types of losses in a transmission line: dielectric substrate losses and conductor losses. In this paper, we propose using air-gap structures to overcome the losses due to the dielectric substrate. This approach needs one pair of glass bumps to make connection between the glass superstrate and silicon motherboard. However, the bump also could contribute undesirable losses. To verify the bump losses, a comparison between a CPW fabricated on a glass motherboard and an AGML on glass was performed. The loss analysis is based on the extracted two-port  $S$ -parameters, and converted into propagation constants using the even- and odd-mode method [14]. The measurement results, shown in Fig. 4, confirm that the losses due to the bump are negligible. Fig. 5 shows the attenuation of the three different transmission lines. The CPW configuration has more than 4-dB/cm losses compared to the two air-gap structures at  $L$ -band. The AGCPW structure also shows slightly more losses compared to the AGML structure. This is because the electric field interacts with the electrons in the doped silicon substrate over the  $240\text{-}\mu\text{m}$  ground spacing. The losses in air-gap configurations, shown in Fig. 5, originate from two sources: The air-gap transmission lines and the two  $500\text{-}\mu\text{m}$  microwave launchers at the line extremities. In order to verify their effects, the  $S$ -parameters of a  $1000\text{-}\mu\text{m}$ -long CPW was extracted from

Fig. 4. Measured losses of the CPW and AGML on glass motherboard to verify the bump losses.

Fig. 5. Measured losses of the three different transmission-line configuration with 5000-mm-long signal lines.

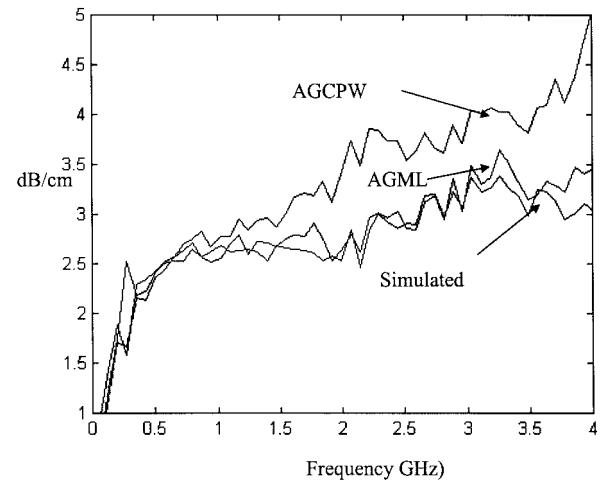

the measurement, and conductor losses due to additional 4000- $\mu\text{m}$ -long signal lines are taken into account in the following measurement. Fig. 6 presents a comparison between measured and simulated losses of the air-gap transmission lines after taking into account the effects of the microwave launchers and conductor losses. The measured and simulated results agree within 0.1-dB/cm range for AGML structure. However, the measured and simulated results for the AGCPW structure show more than 0.5-dB/cm difference above 2 GHz. The difference in the AGCPW case is mainly due to neglecting the wave-electron interaction and recombination process that occurs at the 240- $\mu\text{m}$  open spacing.

## V. APPLICATIONS

### A. Spiral Inductors on Glass

To further explore the advantages of the GMBB technique for MMIC applications, several one-port spiral inductors

Fig. 6. Measured and simulated losses of the AGML, and AGCPW.

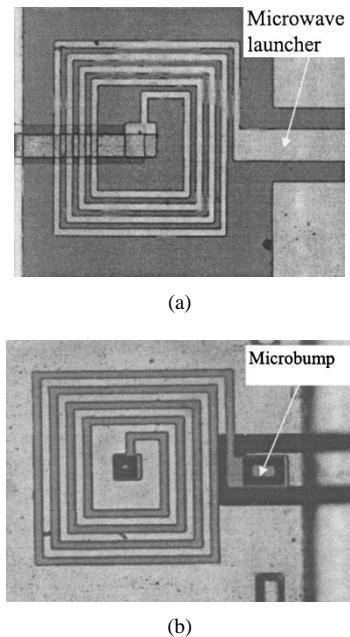

Fig. 7. (a) Conventional CPW structure spiral inductor on a silicon substrate. (b) AGML structure spiral inductor using glass microbump bonding.

using AGML configurations are fabricated and compared with conventional spiral inductors on silicon. Fig. 7(a) shows a typical conventional CPW spiral inductor, and Fig. 7(b) shows a typical 4-1/2-turn AGML spiral inductor. There are several important factors that affect an inductors' performance, including the quality ( $Q$ ) factor and resonant frequency ( $f_R$ ) [15]. High  $Q$  inductors are always desirable. Furthermore, inductors with higher resonant frequency could extend the inductors operation frequency range. The inductor's resonant frequency is limited by the stray capacitances of the inductive structure.

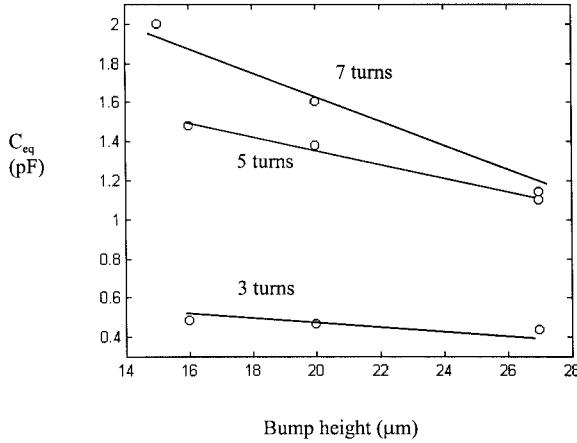

In this paper, a short-open-load one-port calibration routine is used. The one-port  $S$ -parameters were first extracted from an HP8510A network analyzer and converted into  $Z$ -parameters. Both the inductance and resonant frequency values were obtained from the reactive part of the  $Z$ -parameter and translated into the equivalent capacitance for each sample. The equivalent

Fig. 8. The parasitic capacitance values for different turns of AGML inductors with different bump heights.

capacitance is obtained using

$$C_{\text{eq}} = \frac{1}{L \cdot \omega_{\text{res}}^2} \quad (1)$$

where  $\omega_{\text{res}}$  is the resonant frequency. The parasitic capacitance values for different turns of AGML inductors with different bump heights are presented in Fig. 8. Careful examination of Fig. 8 reveals that the capacitance of each inductor can be modeled as follows:

$$C_{\text{eq}} = K_1 \frac{\varepsilon_{\text{eff}1}}{d} + K_2 \frac{\varepsilon_{\text{eff}2}}{s} \quad (2)$$

where  $\varepsilon_{\text{eff}1}$  is signal-to-ground effective dielectric constant,  $\varepsilon_{\text{eff}2}$  is the line-to-line effective dielectric constant,  $d$  is the ground-to-signal line separation,  $s$  is the line-to-line separation, and  $K_1$  and  $K_2$  are constants. They are geometry dependent. It should be noted that  $\varepsilon_{\text{eff}2}$  can be approximated as the average of the dielectric constant of the two materials adjacent to the line. The distance  $d$  is equal to the bump height for the AGML inductors. On the right-hand side of (2), the first term is closely related to  $C_s$ , which is the equivalent signal-to-ground capacitance. Also, the second term is closely related to  $C_p$ , which is the line-to-line capacitance. Due to the distributed nature of the inductor, both terms contribute capacitive effects that limit the inductor operating frequency.

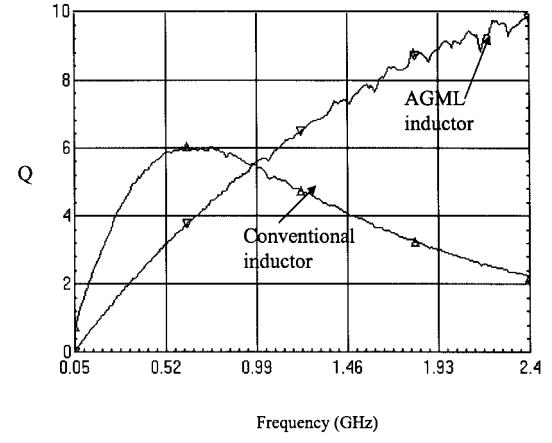

In this paper, the conventional inductor fabricated on a doped silicon substrate has a 6- $\mu\text{m}$ -thick  $\text{SiO}_2$  layer to reduce the high-frequency signal penetration into the lossy substrate. Fig. 9 shows the typical  $Q$  factors of a conventional inductor and an AGML inductor. The conventional inductor has a  $Q_{\text{max}} \approx 6$  at 0.7 GHz, and the AGML inductor has a  $Q_{\text{max}} \approx 10$  at 2.4 GHz. This demonstrates the low-loss advantage of the AGML structure. However, the inductance values of the AGML structure are about 60%–70% of that of the conventional inductor. This is due to the magnetic flux flowing between signal line and ground plane in the AGML inductor, which is smaller than that of the conventional inductor. Hence, increasing the glass bump height can enhance both the inductance values and the resonant frequency performance of AGML inductors.

Fig. 9.  $Q$  factors of a conventional spiral inductor and an AGML structure spiral inductor.

(a)

(b)

Fig. 10. Application of glass microbump bonding for optoelectronics IC's. (a) Light off. (b) Light on.

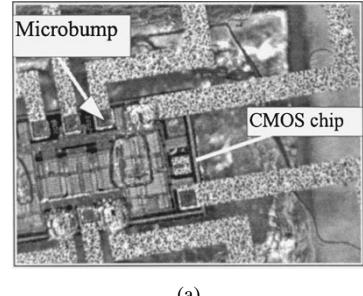

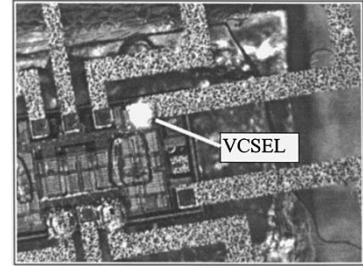

### B. Optical Transmitter Using Glass for OEIC's

In addition to the numerous advantages for the air-gap transmission lines in MMIC's applications, they possess other interesting characteristics that make them favorable for OEIC application. To demonstrate the feasibility of using GMBB for OEIC applications, an optical transmitter is fabricated, as shown in Fig. 10. This optical transmitter circuit is fabricated using the GMBB method to bond the substrate-removed GaAs VCSEL's [16] onto a Motorola CMOS inverter chip. This integration technique has the advantage of combining both highly developed digital silicon CMOS and matured GaAs optoelectronic technologies in a small package. The modulated laser light can be passed through the glass superstrate and coupled into a waveguide or free space. Low-loss air-gap transmission lines can be used for impedance matching between the driving circuit and laser diode. This approach demon-

strates the feasibility of high-density OEIC packaging for the development of two-dimensional optical interconnects [17].

## VI. CONCLUSIONS

This paper presented a new bonding technique, which provides a new integration approach for MMIC's and OEIC's. Two types of air-gap transmission lines deposited on glass superstrates were analyzed, fabricated, and tested. Both the theoretical and experimental results proved that the air-gap transmission lines can reduce losses and parasitic capacitances, compared to conventional CPW interconnects. Furthermore, the transmission characteristics of both air-gap configurations are significantly less affected by the semiconductor surface conditions and bulk substrate properties.

Several inductors were fabricated using the new technology. They exhibit lower parasitic capacitances and higher resonance frequencies, which leads to higher operation range. The new bonding technique is compatible with both silicon and GaAs technologies. Hence, its usage is very promising in overcoming some of the limitations in current MMIC and OEIC applications.

## ACKNOWLEDGMENT

The authors would like to thank Dr. G. Maracas, Dr. R. Droopad, Dr. H. Fathollahnejad, Dr. D. Mathine, Dr. D. Schroder, and Dr. D. Allee for the VCSEL's and equipment.

## REFERENCES

- [1] L. M. Burns, "Applications for GaAs and silicon integrated circuits in next generation wireless communication systems," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1088-1095, Oct. 1995.

- [2] L. M. Devlin, B. J. Buck, J. C. Clifton, A. W. Dearn, and A. P. Long, "A 2.4-GHz single chip transceiver," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp.*, Atlanta, GA, June 1993, pp. 23-26.

- [3] R. G. Meyer and W. D. Mack, "A 1 GHz BiCMOS RF front-end IC," *IEEE J. Solid-State Circuits*, vol. 29, pp. 350-355, Mar. 1994.

- [4] C. Marshall, F. Behbahani, W. Birth, A. Fotowat, T. Fuchs, R. Gaethke, E. Heimerl, S. Lee, P. Moore, S. Navid, and E. Saur, "A 2.7 V GSM transceiver IC's with on-chip filtering," in *Int. Solid State Circuits Conf.*, San Francisco, CA, Feb. 1995, pp. 148-149.

- [5] A. Hairapetian, "An 81-MHz IF receiver in CMOS," in *Int. Conf. Solid State Circuits*, San Francisco, CA, 1996, pp. 56-57.

- [6] D. K. Schroder, *Advanced MOS Devices. Modular Series on Solid State Devices*. Reading, MA: Addison-Wesley, 1987.

- [7] J. D. Wynn, G. J. Zydzik, and R. E. Leibenguth, "8 × 18 top emitting independently addressable surface-emitting laser arrays with uniform threshold current and low threshold voltage," *Appl. Phys. Lett.*, vol. 62, pp. 1718-1720, 1993.

- [8] E. Zeeb, T. Hackbarth, and K. J. Ebeling, "High speed performance of 2-D vertical-cavity laser diode arrays," *IEEE Photon. Technol. Lett.*, vol. 6, pp. 1056-1058, Sept. 1994.

- [9] R. Olbright, J. L. Jewell, R. P. Bryan, and W. S. Fu, "Micro-optic and microelectronic integrated packaging of vertical cavity laser arrays," *Proc. SPIE*, vol. 1851, pp. 97-105, 1993.

- [10] C. Y. Chi, and G. M. Rebeiz, "Planar millimeter-wave microstrip lumped elements using micro-maching techniques," in *IEEE MTT-S Symp. Dig.*, San Diego, CA, May 23-27, 1994, pp. 657-660.

- [11] A. C. Reyes, S. M. El-Ghazaly, S. Dorn, M. Dydyk, and D. K. Schroder, "Silicon as a microwave substrate," in *IEEE MTT-S Symp. Dig.*, San Diego, CA, May 23-27, 1994, pp. 1759-1762.

- [12] A. C. Reyes and S. M. El-Ghazaly, "Coplanar waveguides and microwave inductors on silicon substrates," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 2016-2021, Sept. 1995.

- [13] T. LaRocca, A. C. Reyes, and S. M. El-Ghazaly, "Analysis of electromagnetic wave propagation on coplanar waveguides on doped semiconductor substrates," in *IEEE Int. Microwave Symp. Dig.*, vol. 1, San Francisco, CA, June 1996, pp. 295-298.

- [14] Y. Shih, "Broadband characterization of conductor-backed coplanar waveguide using accurate on-wafer measurement techniques," *Microwave J.*, pp. 95-105, 1991.

- [15] J. C. P. Chuang, S. El-Ghazaly, N. El-Zien, V. Nair, and G. Maracas, "Low loss air-gap spiral inductors for MMIC's using glass microbump bonding technique," in *IEEE Int. MTT-S Symp. Dig.*, vol. 1, Baltimore, MD, June 1998, pp. 131-134.

- [16] H. Fathollahnejad, S. Daryanani, D. Mathine, C. P. Chuang, R. Droopad, and G. Maracas, "Integration of GaAs vertical-cavity surface emitting lasers into silicon circuitry," in *Proc. IEEE Cornell Conf. on Advanced Concepts High Speed Semiconduc. Devices Circuits*, Ithaca, NY, Aug. 1995, pp. 373-381.

- [17] A. J. Moseley, M. Q. Kearley, R. C. Morris, J. Urquhart, M. J. Goodwin, and G. Harris, "8 × 8 flipchip assembled InGaAs detector arrays for optical interconnect," *Electron. Lett.*, vol. 27, pp. 1566-1567, 1991.

**Jeff C. P. Chuang** (S'89) received the B.S.E.E. degree from the University of Utah, Salt Lake City, in 1991, the M.S.E.E. degree from the University of Wisconsin, Madison, in 1993, and is currently working toward the Ph.D. degree in electrical engineering at Arizona State University (ASU), Tempe.

From 1993 to 1994, he was with Lorals, Palo Alto, CA, as a Circuit Design Engineer, where he designed MMIC's for wireless communication. His research interests include the development and characterization of high-frequency IC's and device physics.

**Samir M. El-Ghazaly** (S'84-M'88-SM'91) received the Ph.D. degree in electrical engineering from the University of Texas at Austin, in 1988.

In 1988, he joined Arizona State University (ASU), Tempe, where he is currently a Professor in the Electrical Engineering Department. He has been with several universities and research centers, including the College of Engineering, Cairo University, Egypt, as a Teaching Assistant and Assistant Lecturer, the Centre Hyperfréquences et Semiconducteurs, Université de Lille I, France,

where he worked on the simulation of submicron-gate MESFET's, the University of Ottawa, Ont., Canada, where he worked on the analysis of *E*-plane circuits, the University of Texas at Austin, first as a Research Assistant and then as a Post-Doctoral Fellow, NASA, Jet Propulsion Laboratory, Pasadena, CA, where he was a Summer Faculty Research Fellow working on millimeter-wave mixers, CST-Motorola, Inc., Tempe, AZ (while on sabbatical leave from ASU), where he worked on modeling semiconductor devices for RF applications, and IEMN, Université de Lille, France, as a Visiting Professor. His research interests include microwave and millimeter-wave semiconductor devices and passive circuits, semiconductor device simulations, ultrashort pulse propagation, linear and nonlinear modeling of superconductor microwave lines, wave device interactions, EM's, and numerical techniques applied to MMIC's. He is an elected member of Commissions A and D of URSI, and is secretary of the U.S. National Committee of URSI, Commission A.

Dr. El-Ghazaly is a member of Tau Beta Pi, Sigma Xi, and Eta Kappa Nu. Since 1991, he has been a member of the Technical Program for the IEEE International Microwave Symposium, and is on the editorial board of the *IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES*. He was the chairman of the IEEE-Wave and Devices Group, Phoenix Section, chapter funding coordinator for IEEE MTT-S, and is currently the general chairman of the upcoming IEEE MTT-S 2001 International Microwave Symposium.